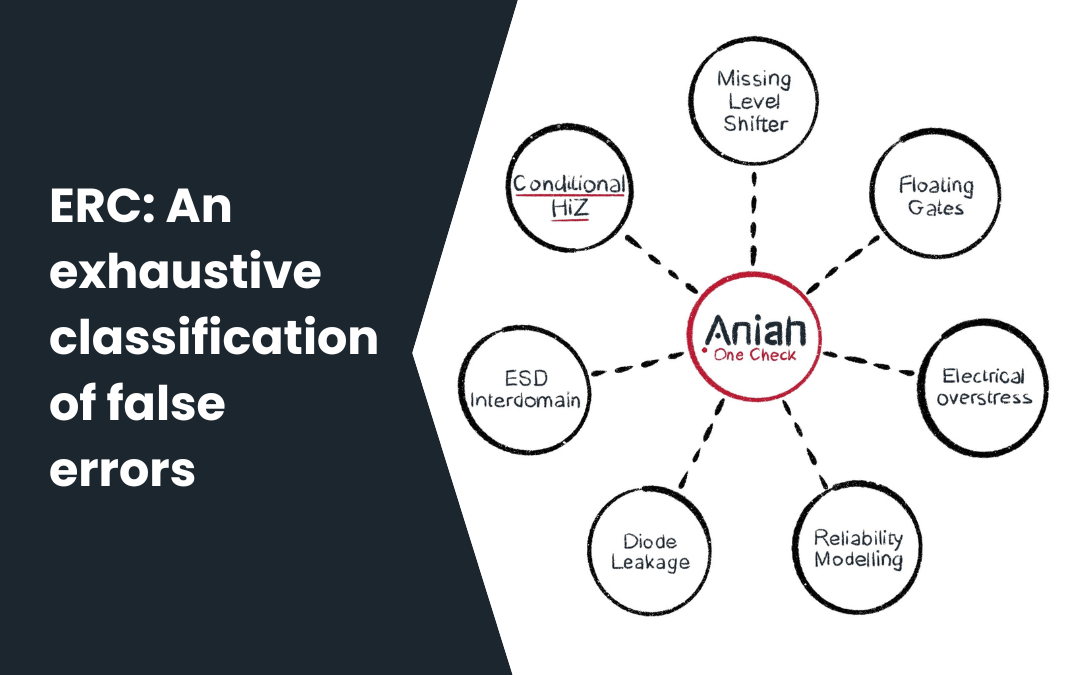

Consequently, considerable effort is made throughout the design flows to avoid electrical errors from occurring in the first place. Experience, however, shows that without a verification solution dedicated to the analysis of electrical circuits at the chip scale, some errors elude the vigilance of design engineers, even with the most comprehensive design flows.

Those errors have severe consequences, ranging from delays in the project schedule (thus increasing its cost), failed time-to-market and in the worst case, product recalls (and the major financial as well as brand image impacts this can imply).

In this document, we go over why chips routinely go to fab with undetected electrical errors and the consequences that such errors have on a chip project success and lifetime.